Reverse engineering hardware for software reversers: studying an encrypted external HDD

Joffrey Czarny & Raphaël Rigo / AGI / TX5IT 2015-10-02 / Hardwear.io

#### Introduction

### Why study encrypted hard drives?

- Initially: audit need inside Airbus Group

- Previous work revealed vulnerabilities

- Discover how to analyze hardware based on microcontrollers

### Previous epic fails on this type of HW

- Kingston/SanDisk FIPS 140-2: magic unlocking packet (2010)

- Corsair Padlock: data not encrypted, reachable without PIN (2008)

- Corsair Padlock 2: brute-forceable PIN (2010)

- WD Passport (yesterday's talk by Gunnar Alendal and Christian Kison)

### End goal

- Analyze the actual level of protection of user data

- ⇒ Validate security and cryptography implementations inside the enclosure

#### Introduction

### This talk's objectives:

- Describe the study of an external encrypted HDD:

- Explain the methodology in details

- Show our various failures

- Give leads to continue the analysis

### Case study: Zalman ZM-VE400

- Enclosure: HDD is replaceable

- Optional AES-256 XTS encryption (physical keyboard)

- Can "mount" ISO as USB optical drive

- Really a rebranded iodd 2541

### Context, first results

### General security checks

- Verify basic crypto properties:

- ECB mode? statistical tests OK?

- Fixed key?

- More tests, to verify the key is not derived directly from the PIN:

- The same PIN, on 2 different enclosures, **must** lead to different encryption

- The same PIN, on the same enclosure, must lead to different encryption

- Secret material (keys, hashes) should be stored in tamper resistant hardware

#### VE400 results

- Basic crypto properties: OK

- Encryption does not depend on enclosure: an encrypted HDD put in a new Zalman enclosure can be accessed with the right PIN

- Activating encryption uses 10 sectors at the end of the HDD:

- Not usable anymore

- Contain a blob of 768 bytes, of high entropy, twice

## **Going forward**

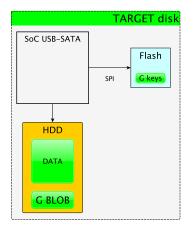

### Important result: design failure

Everything needed to decrypt data is stored on the HDD itself.

⇒ Efficient attacks are possible (*bruteforce*, key recovery)

### New end goal

Understand the blob stored at the end of the disk: its data and its format, to implement an offline attack

#### How?

First by trying to access the *firmware* and/or by analyzing communications Firmware updates are encrypted, so we need to attack the hardware

## Hardware analysis

### PCB analysis

- Components identification

- Traces and vias identification

- ⇒ Logical view

### Flash memories study

- Identify communication buses

- Flash content recovery

- ⇒ Flash content analysis (hopefully cleartext code)

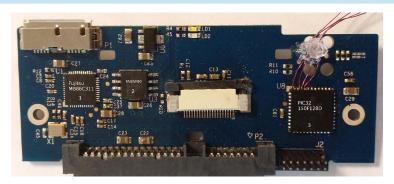

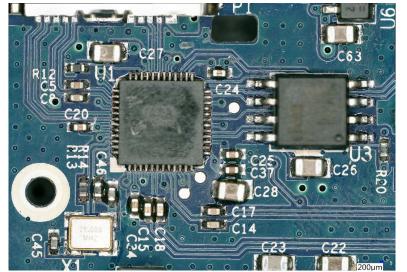

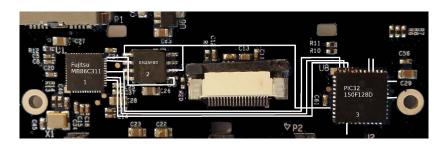

### PCB: component identification 1/2

#### PCB: front side

- System on Chip (SoC) Fujitsu MB86C311 USB3-SATA

- SPI flash FN25F80

- PIC32MX 150F128D microcontroller

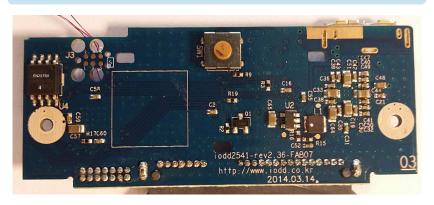

## PCB: component identification 2/2

### PCB: back size

SPI flash EN25F80

#### SoC and microcontroller

#### Fujitsu MB86C311

- USB3⇔SATA controller

- AES-256 XTS encryption

- ARM core

- Internal ROM and external SPI firmware support (encrypted?)

### PIC32MX 150F128D

- MIPS32 CPU (with MIPS16e support)

- 128 Ki of internal flash

- 32 Ki of RAM

- Supports ICSP and EJTAG

- Protection bits to disable external access

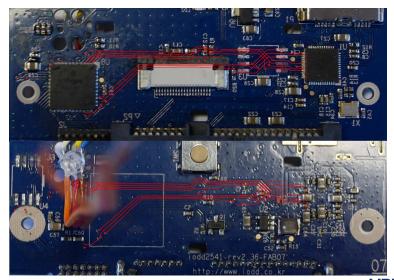

## PCB: traces analysis (1/5): Hobo mode with GIMP

## PCB: traces analysis (2/5): getting real with PCBRE [5]

# PCB: traces analysis (3/5): leveling up: optical microscope

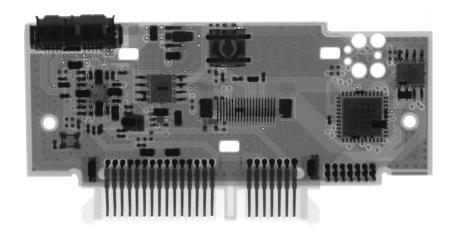

## PCB: traces analysis (4/5): level cap: X-rays

## PCB: traces analysis (5/5)

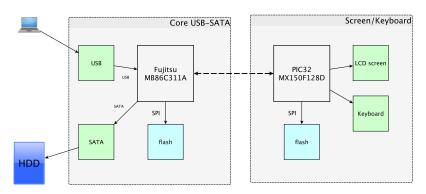

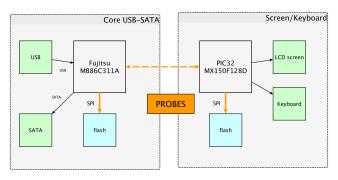

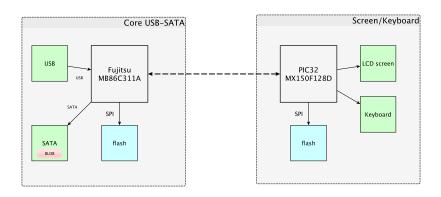

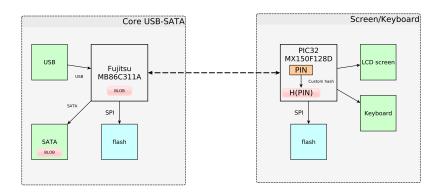

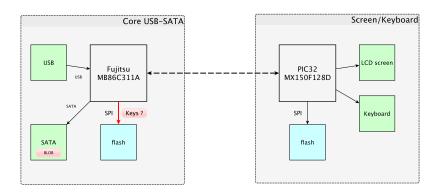

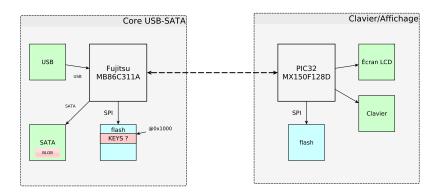

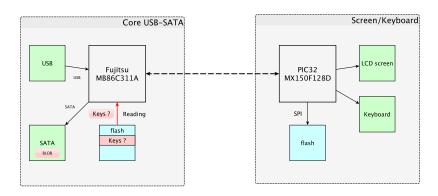

#### In the end

- One flash dedicated to the USB-SATA controller (SoC)

- One flash dedicated to the PIC32

- One link between the SoC and the PIC, (partially) shared with the SoC flash

## **PCB: logic view**

### What's inside the flash chips?

Maybe the code is in cleartext?

⇒ Let's get their contents!

## Flash content recovery (1/2)

### Reading flash content

- SPI

- Chip desoldering needed to avoid interferences

- Interface using a SOIC→DIP adapter to keep the board working

## Flash content recovery (2/2)

#### SPI tools

- GoodFET with goodfet.spiflash (recommended)

- Bus Pirate

- Raspberry Pi with spidev

#### Results: flashes content

#### **USB-SATA** controller:

- Plaintext configuration data (USB descriptors, etc.)

- Code, encrypted

#### PIC32 microcontroller:

- A font, for the LCD screen

- Code, encrypted

#### Results

#### Code access: fail

All the code is encrypted, so we cannot reverse engineer the firmware

#### What can we do now?

As in network reversing, we will analyze communications (black box)

#### How?

By using a logic analyzer to capture communications

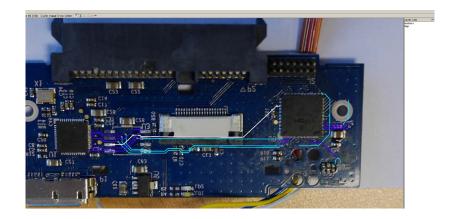

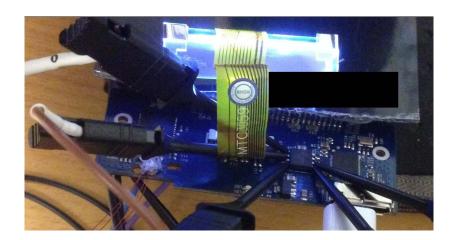

## Hardware and probe placement

Saleae Logic Pro 16 logic analyzer

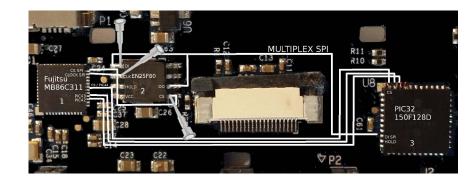

# PCB traces and components pinout

# **Probe placement**

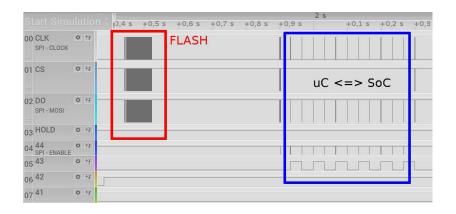

#### **Screenshot**

# **Analyzing flash SPI communications**

#### USB-SATA/PIC to flash

- Placing the 4 probes: simply on flash pins

- SPI decoding parameters: "standard" (cf. datasheet)

- Sampling speed: 50MS/s min, 100MS/s recommended (25MHz quartz)

#### Post-treatment

- CSV export of decoded SPI data

- Ruby script to interpret flash commands:

- Text display

- Binary dump rebuilding

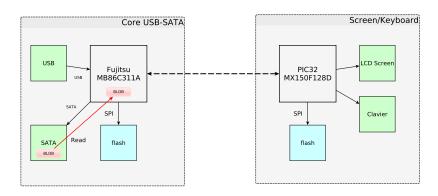

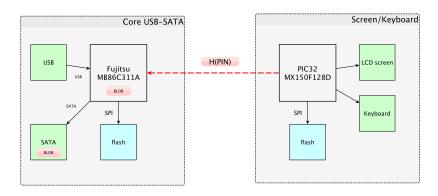

#### Results

- PIC never writes to its external flash

- USB-SATA controller writes data when the PIN is validated

# **Analyzing SoC** ↔ **PIC communications**

#### USB-SATA controller ↔ PIC

- Probes placement: on the SOC flash pins (cf. PCB traces)

- Sampling speed: 50MS/s min, 100MS/s recommended

- Protocol: unknown

#### Post-treatment

SPI based protocol:

- Low level decoding with Saleae, then CSV export

- Application-layer data must be reversed engineered

## **Custom protocol**

### Reverse engineering

- $\bullet$  Preambles: AA AA AA AA 55 (SoC  $\rightarrow$  PIC) and A5 A5 5A (PIC  $\rightarrow$  SoC)

- Type, Length, Value

- Frames are numbered and acknowledged

- Unknown 16bits checksum

- ⇒ Ruby script to decode data from the CSV produced by Saleae

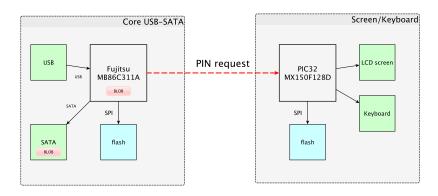

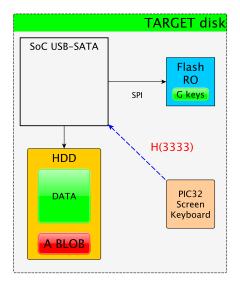

### Decoded example: PIN request

```

0.00000000 SoC->PIC T: 0x33, ID: 0x14 | 01,01,10,01

0.00003861 PIC->SoC RESP: 0x14 | 06,00,01,00,09,4d,01,cb,

0e,00,00,00,89,0f,3a,7a

```

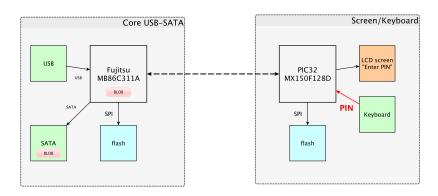

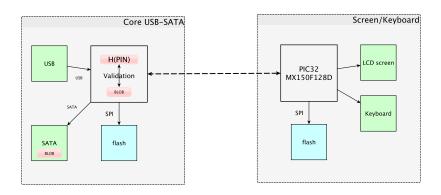

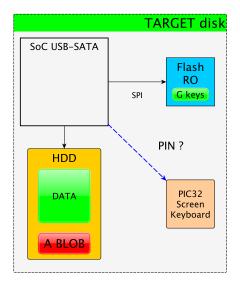

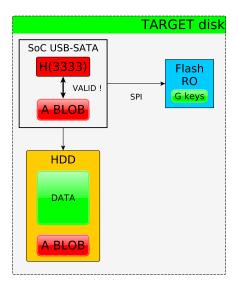

# **Summary: communication sequence**

# **Summary: communication sequence**

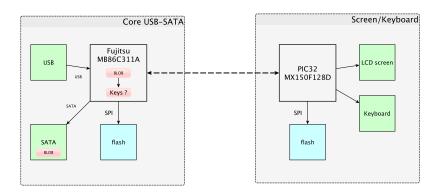

#### And now?

### Remaining questions

- Can we do a hardware bruteforcer? (PIC+Keyboard emulator)

- No, because the hash algorithm is unknown

- What is inside the block at 0x1000 in the SoC flash?

#### Flash block at 0x1000

### Properties:

- Written when:

- Enabling encryption

- Entering a valid PIN

- Erased when encryption is disabled

- Contains 3 different blocks of data of high entropy:

- 1. 512 bits, AES-256-XTS key 1, encrypted?

- 2. 512 bits, AES-256-XTS key 2, encrypted?

- 3. SHA256 of previous data (1 and 2)

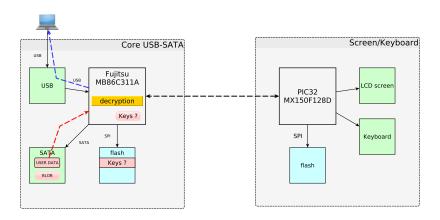

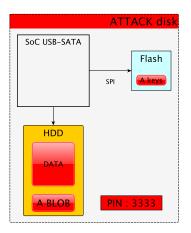

# **Designing an attack**

### Hypothesis

The block at 0x1000 seems to **contain AES-XTS encryption keys**, in an encrypted or obfuscated form

### Implications?

Can we use this block to mount an attack?

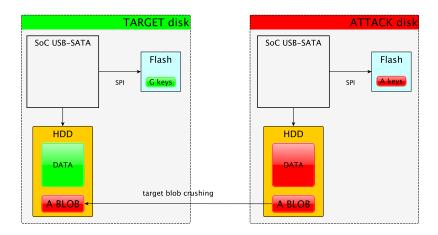

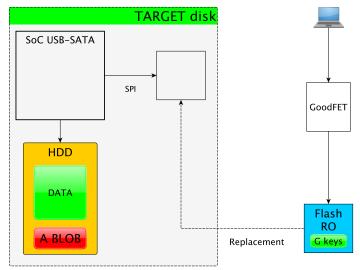

### The idea

Assuming the block at 0x1000 contains decryption keys:

- We will try to keep the one of the target drive intact, in the flash ...

- while validating the PIN against a chosen blob, stored on the HDD

### In practice

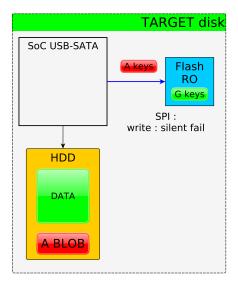

#### First fail

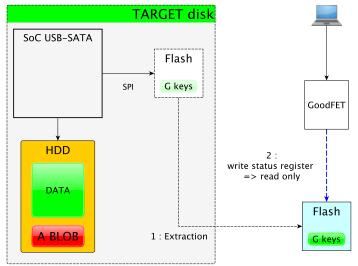

The flash status register is reset to 0 during startup

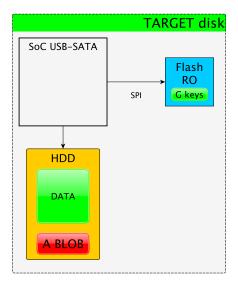

### Attack, second version

The flash is put in read only after startup:

- 1. Connect the enclosure

- 2. Unplug flash

- 3. Put it in read only using GoodFET

- 4. Plug it back

- 5. Continue the attack: enter the known PIN

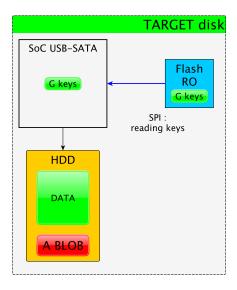

### Final result

Fail. PIN code is not valid (Not match on screen)

⇒ There's probably an unidentified check

### Final attack: demo

### Conclusion

### Encrypted data security

The whole security relies on:

- The security of the blob at the end of the disk

- The security of the block at 0x1000 in the flash

- ⇒ Everything relies on the fact that the Fujitsu firmware is "secret"

### iodd's feedback (original board dev)

Firmware evolution (version 077):

PIN hash is now non-deterministic

The rest is not fixable:

- Customer support choice: data can survive broken enclosure

- Opaque handling of the blob at the end of the HDD: binary code provided by Fujitsu

# **Conclusion: going further**

### Access the code of the USB-SATA controller

- Find a JTAG? (unlikely)

- The firmware encryption is the same on all chips:

- "Buy" the SDK? (probable NDA)

- Find someone generous ;)

### Emulate the SoC SPI flash

- Allows subtle modifications of block 0x1000

- Try blind ARM code modifications

### Dump PIC32 code

Use semi-invasive attack to reset protection fuse

⇒ Hardware bruteforcer by emulating the whole keyboard/screen part

**End**

# Questions?

### References

- [1] http://support.ironkey.com/article/AA-02513/

- [2] http://www.h-online.com/security/features/ USB-stick-with-PIN-code-746169.html

- [3] https://www.exploit-db.com/papers/15424/

- [4] http://hardwear.io/speakers-kison-alendal/

- [5] https://github.com/davidcarne/pcbre

- [6] http://sigrok.org/wiki/Main\_Page

- [7] http://support.saleae.com/hc/en-us/articles/200672010

# **Blob comparison**

```

bloc ssd

bloc toshiba

```

## Firmware comparison: Zalman vs PS4

```

flash controlerSATA

3A 93 23 4C

7C 7A BB CD C3 19

75 43 10 D5 5B 22 7D 86

0000 2120: 01 31 47 D6 9B 97 4F F1

3A 01 87 DC C6 50 18 95

0000 2130: D7 0E 75 E0 17 83 32 A0

19 3D 46 5A DC 44 88 DF

9000 2140: E4 D0 84 89 86 FC 9B BD

0000 2150: 96 2D D2 5C 5C F4 4C E8

9000 2160: 94 BD 16 44 49 C3 54 36

76 A6 4A D1 5D 4C BE E0

9000 2170: FF 60 7D 96 D3 DD 9C C7

9A 69 C0 60 C7 7F EB 8F

D7 23 7E 1F 98 10 00 4D

0000 2190: 53 8D CF 14 50 32 6C 6E

82 C6 E1 06 2B C6 22 B4

0000 21A0: 8A 23 FD FB F4 46 0F 15

02 FF 45 0A 77 59 A3 9B

PS4 dump.bin

9000 2100: 0E 93 D1 03 74 37 BB D1

1C C9 DF 95 EC 7C 73 37

87 DC C6 50 18 95

19 3D 46 5A DC 44 88 DF

FA D7 F1 BE C5 79 EF C4

9000 2150: 96 2D D2 5C 5C F4 4C

0000 2160: 94 BD 16 44 49 C3 54 36

76 A6 4A D1 5D 4C BE E0

0000 2170: FF 60 7D 96 D3 DD 9C C7

9A 69 C0 60 C7 7F EB 8F

0000 2180: DE F1 0E CB 7F C9 55 28

D7 23 7E 1F 98 10 00 4D

9000 2190: 53 8D CF 14 50 32 6C 6E

82 C6 E1 06 2B C6 22 B4

0000 21A0: 8A 23 ED EB F4 46 0F 15

02 EF 45 0A 77 59 A3 9B

.#...F.. ..E.wY..

```